- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-SDRAM/DDR2 (Altera)IP DDR2 SDRAM CONTROLLER

�� �

�

�

�3–14�

�f�

�Chapter� 3:� Functional� Description�

�Device-Level� Description�

�For� Stratix� II� devices,� if� you� turn� on� the� Use� fed-back� clock� option� and� the� Enable�

�DQS� mode� option,� you� enable� fed-back� resynchronization,� which� uses� a� fed-back�

���the� data� back� to� the� system� clock.�

�Turning� off� Enable� DQS� mode� enables� fed-back� capture� mode.� This� mode� uses� a�

�fed-back� clock� to� capture� the� read� data� and� does� not� use� the� DQS� strobe� for� capture�

�(refer� to� Figure� A–4� on� page� A–8� ).� A� resynchronization� phase� from� the� system� PLL� is�

�required� to� safely� transfer� the� captured� data� to� system� clock� phase.� This� mode� offers�

�lower� performance� than� fed-back� resynchronization,� but� allows� greater� flexibility� in�

�your� choice� of� pins� for� DQ� and� DQS.�

��For� more� information� on� non-DQS� mode,� refer� to� Figure� A–2� on� page� A–6� and�

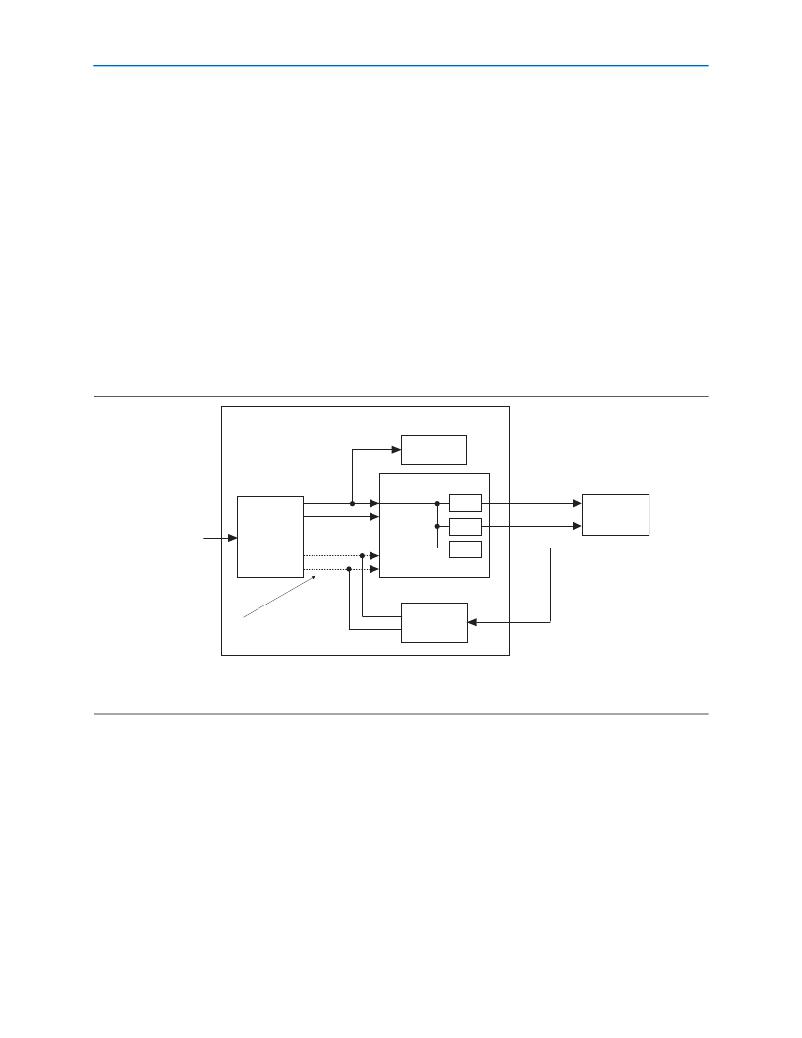

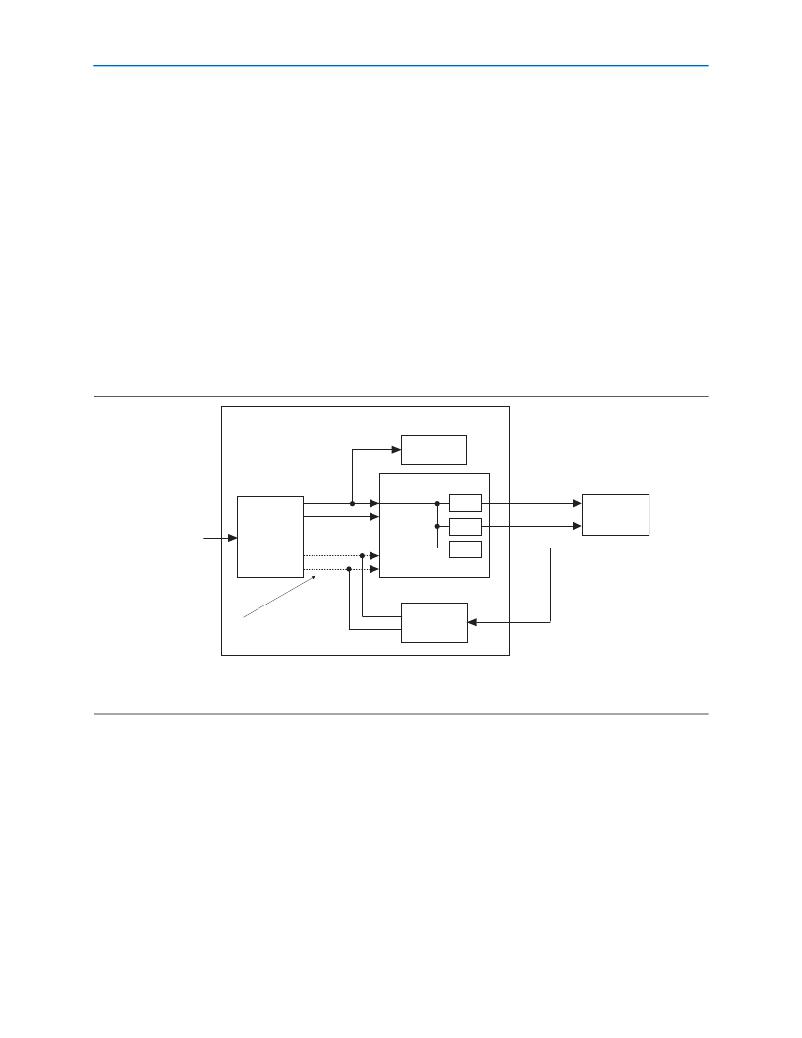

��Figure� 3–8.� Stratix� II� PLL� Configuration�

��Stratix� II� De� v� ice�

�Stratix� II� DLL�

�DDR� SDRAM�

�C0�

�C1�

�clk�

�write_clk�

�Controller�

�altddio�

�clk_to_sdram_n�

�clk_to_sdram�

�DDR� SDRAM�

�altddio�

�clock_source�

�Enhanced� PLL�

�C2�

�resynch_clk� or�

�capture_clk�

�altddio�

�fedback_clock_out�

�C3�

�postamble_clk�

�Optional�

�Note� 1�

�Fed-Back� Clock�

�PLL�

��(1)� In� most� cases,� clk� or� write_clk� are� used� as� the� resynchronization� and� postamble� clocks,� therefore� you� need� not� use� a� separate� clock� output�

�from� the� PLL.�

��Stratix� GX� devices.�

�1�

�The� dqs_ref_clk� input� for� Stratix� or� Stratix� GX� devices� can� be� either� fed-back� from�

�the� clock� output� driving� the� SDRAM� or� a� separate� clock� output� from� the� PLL.� The�

�phase� of� dqs_ref_clk� relative� to� the� other� clocks� in� the� system� is� unimportant.� The�

�controller� switches� off� this� input� during� reads,� if� you� turn� on� Switch� off� Stratix� DLL�

�reference� clock� during� reads� (refer� to� “Manual� Timing� Settings”� on� page� A–1� ).�

��?� March� 2009� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-SLITE2

IP SERIALLITE II

IP-SRAM/QDRII

IP QDRII SRAM CONTROLLER

IP-VITERBI/SS

IP VITERBI LOW-SPEED

IP4220CZ6,125

IC USB DUAL ESD PROTECT 6TSOP

IPA-66-1-600-10.0-A-01-T

CIRC BRKR 10A 2POLE SCREW TERM

IPR-CSC

IP COLOR SPACE CONVERTER RENEW

IPR-ED8B10B

IP 8B10B ENCODER/DECODER RENEW

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

相关代理商/技术参数

IP-SDRAM/DDR3

功能描述:开发软件 DDR3 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR

功能描述:开发软件 DDR SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/LPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPSE.4.33SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50)

IPSE.4.62SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50)

IPS-EMBEDDED

功能描述:开发软件 Embedded IP Suite MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPS-EVAL-EH-01

功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP